1. Introduzione

Gli oscillatori al quarzo generano segnali di clock altamente stabili, necessari in quasi tutti i sistemi elettronici, dai semplici circuiti dei microcontrollori ai sistemi di trasmissione dati ad alta velocità.

Il segnale di uscita di un oscillatore deve essere compatibile con la famiglia logica o l'interfaccia a valle. Nel corso dei decenni si sono sviluppati diversi standard di uscita, ciascuno adattato alle esigenze della propria epoca e applicazione.

Questo documento fornisce una panoramica completa dei sette tipi di segnale di uscita più comuni negli oscillatori al quarzo: CMOS, TTL, onda sinusoidale troncata, seno, LVPECL, LVDS e HCSL.

Per ogni tipo vengono illustrati lo sviluppo storico, le caratteristiche elettriche, la forma d'onda tipica e i campi di applicazione preferiti.

2. Sviluppo storico

Lo sviluppo dei tipi di segnale di uscita è strettamente legato all'evoluzione della tecnologia dei semiconduttori e alle crescenti esigenze in termini di frequenze di clock e integrità del segnale:

2.1 TTL (Logica Transistor-Transistor) – dal ca. 1964

Il TTL è stato uno dei primi standard logici digitali ampiamente diffusi ed è stato introdotto da Texas Instruments come serie 7400. Gli oscillatori con uscita TTL funzionano con una tensione di alimentazione di 5 V e forniscono intervalli di livello direttamente compatibili con le porte TTL. Lo standard ha plasmato l'elettronica digitale per decenni ed è stato lo standard logico dominante fino agli anni '90.

2.2 CMOS (Complementary Metal-Oxide-Semiconductor) – dal ca. 1968

La tecnologia CMOS è stata originariamente sviluppata da RCA ed è caratterizzata da un consumo di corrente a riposo estremamente basso. Gli oscillatori CMOS forniscono segnali di uscita rail-to-rail, ovvero l'uscita oscilla quasi interamente tra 0 V e VCC. Con la continua miniaturizzazione e la tendenza verso tensioni di alimentazione più basse (3,3 V, 2,5 V, 1,8 V), CMOS è diventato lo standard di uscita più utilizzato per gli oscillatori al quarzo.

2.3 Sinus – dagli albori della tecnica degli oscillatori

I segnali di uscita sinusoidali sono antichi quanto la tecnologia degli oscillatori. Gli oscillatori al quarzo oscillano fisicamente in modo sinusoidale; tutte le altre forme d'onda sono generate da circuiti a valle. Le uscite sinusoidali sono preferite nella tecnologia ad alta frequenza, negli strumenti di misura e nell'elaborazione dei segnali analogici perché non generano armoniche.

2.4 Clipped Sine Wave – dal ca. anni '70

L'uscita Clipped Sine Wave rappresenta un compromesso tra l'uscita sinusoidale e quella ad onda quadra. Il segnale sinusoidale viene limitato (clippato) ai picchi, creando fronti più ripidi rispetto al seno puro ma meno armoniche rispetto a un segnale ad onda quadra. Questo tipo di uscita è stato utilizzato soprattutto nelle telecomunicazioni e nelle applicazioni ad alta frequenza più datate. I circuiti Clipped Sine Wave sono oggi utilizzati principalmente ancora nei TCXO. Con questa tecnologia è possibile realizzare TCXO significativamente più efficienti dal punto di vista energetico rispetto alla tecnologia CMOS. I CSW-TCXO vengono quindi utilizzati come riferimento nei dispositivi di navigazione, nei sistemi di chiamata di emergenza e nei gateway. Ovunque siano necessarie portata del segnale (radio) e un posizionamento ad alta precisione.

2.5 LVPECL (Low-Voltage Positive Emitter-Coupled Logic) – dal ca. anni '90

Con la necessità di frequenze di clock sempre più elevate nei sistemi di rete e telecomunicazione, il LVPECL è nato come logica di uscita differenziale veloce. Il LVPECL si basa sulla classica tecnica ECL (Emitter-Coupled Logic), già sviluppata negli anni '60 per applicazioni ad alta velocità, e la adatta a tensioni di alimentazione più basse (3,3 V anziché -5,2 V). Il LVPECL offre tempi di commutazione estremamente brevi ed è adatto per frequenze ben oltre 1 GHz.

2.6 LVDS (Low-Voltage Differential Signaling) – dal 1994

Il LVDS è stato introdotto nel 1994 come standard ANSI/TIA/EIA-644 e ottimizza la trasmissione differenziale del segnale per un basso consumo energetico e alte velocità di trasmissione dati. La ridotta escursione di tensione differenziale di soli 350 mV consente commutazioni rapide con emissioni elettromagnetiche minime. Il LVDS è oggi ampiamente diffuso nelle interfacce display, nei collegamenti dati seriali e nel clocking FPGA.

2.7 HCSL (High-Speed Current Steering Logic) – dal ca. 2002

L'HCSL è stato sviluppato specificamente per lo standard PCI Express ed è lo standard di clock di riferimento dalla prima generazione PCIe. Il PCI-SIG ha specificato l'HCSL come segnale differenziale basato sulla modalità corrente con escursione di tensione molto bassa, ottimizzato per i clock di riferimento a 100 MHz nei sistemi PCIe. L'HCSL è oggi indispensabile in ogni PC, server e sistema embedded con interfaccia PCIe.

3. Panoramica delle forme d'onda

I seguenti diagrammi mostrano le forme d'onda idealizzate dei sette tipi di uscita. Si notino i diversi intervalli di tensione e le escursioni – questi sono determinanti per la compatibilità con i ricevitori a valle.

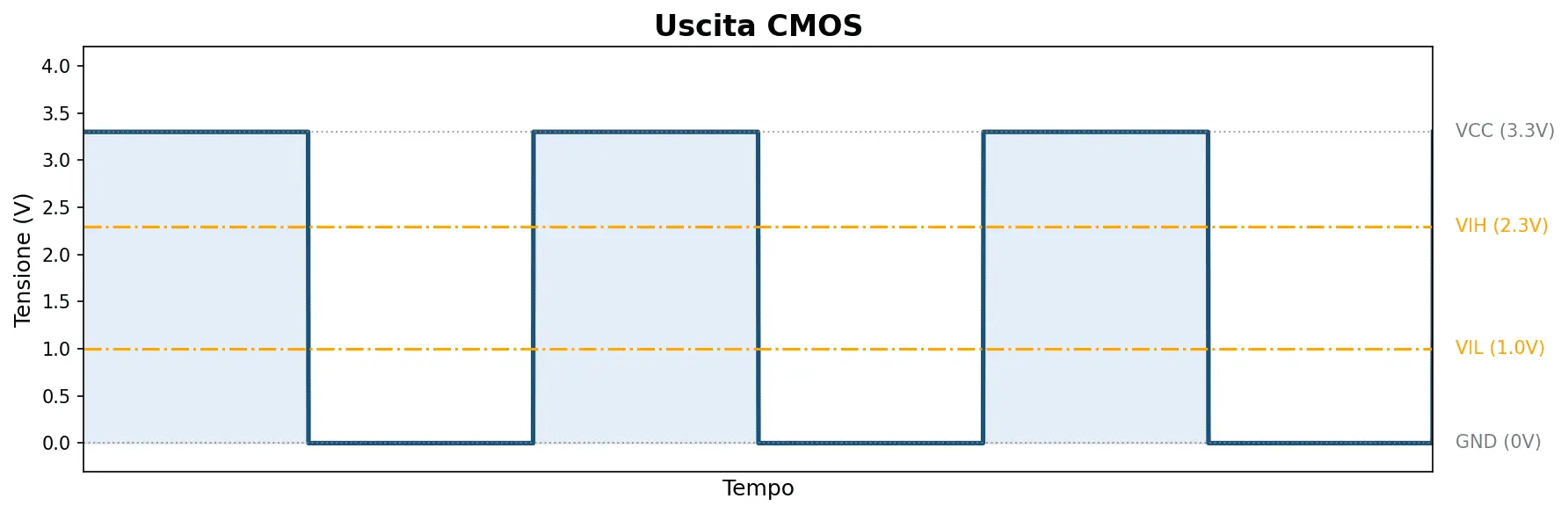

3.1 CMOS

Fig. 1: Segnale di uscita CMOS – Onda quadra rail-to-rail tra 0 V e VCC (qui 3,3 V)

Il segnale CMOS si caratterizza per la sua escursione di tensione completa tra GND e VCC. Le soglie di ingresso VIL e VIH si trovano tipicamente al 30 % e al 70 % di VCC rispettivamente, garantendo un ampio margine di rumore. Le strutture di driver di uscita simmetriche (MOSFET canale P/canale N) consentono tempi di salita e di discesa pressoché uguali.

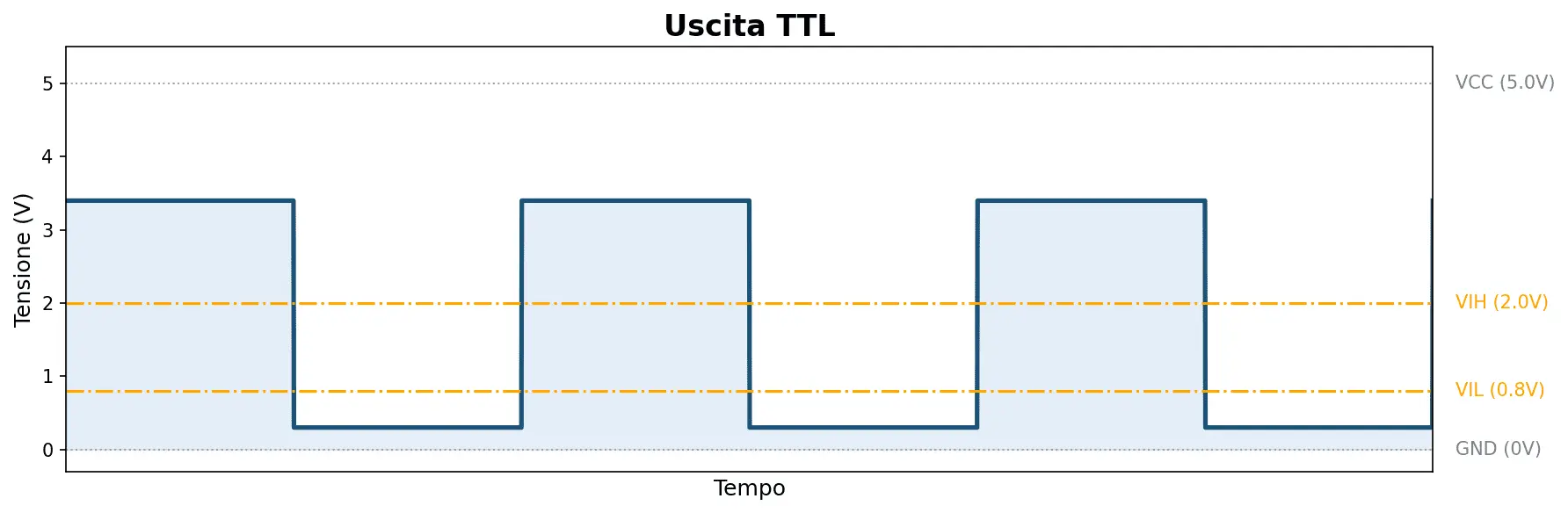

3.2 TTL

Fig. 2: Segnale di uscita TTL – VOH tipicamente 3,4 V, VOL tipicamente 0,3 V a 5 V di alimentazione

A differenza delle uscite CMOS, i transistor TTL non raggiungono livelli rail-to-rail. Il livello alto (VOH) è tipicamente 3,4 V (minimo 2,4 V) e il livello basso (VOL) è massimo 0,4 V. Le soglie asimmetriche (VIL = 0,8 V, VIH = 2,0 V) derivano dall'architettura del transistor bipolare. Il cosiddetto "intervallo proibito" tra 0,8 V e 2,0 V non deve essere assunto durante il funzionamento statico.

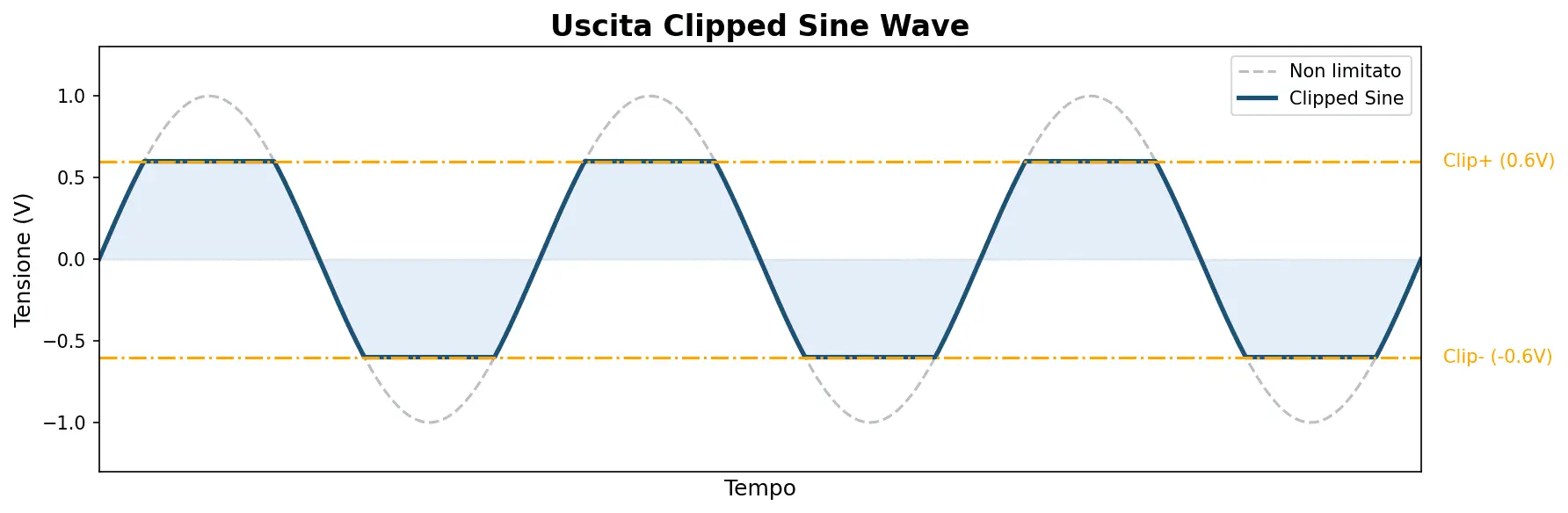

3.3 Clipped Sine Wave

Fig. 3: Uscita Clipped Sine Wave – Segnale sinusoidale con picchi di ampiezza limitati

Con l'uscita Clipped Sine Wave, il segnale sinusoidale naturale del risonatore al quarzo viene limitato a soglie definite. La linea tratteggiata mostra la forma sinusoidale non limitata. Il clipping crea attraversamenti dello zero più ripidi rispetto al seno puro, facilitando il pilotaggio della logica a valle, mentre il contenuto armonico rimane moderato.

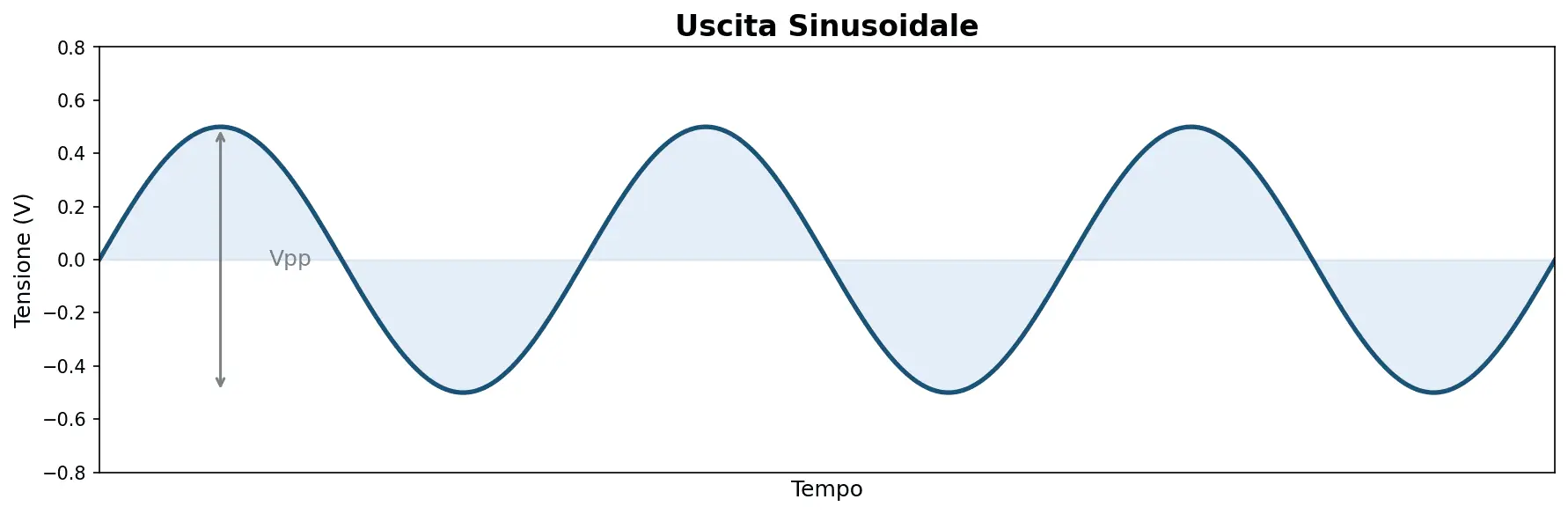

3.4 Sinus

Fig. 4: Uscita sinusoidale – Segnale sinusoidale puro con tensione picco-picco definita (Vpp)

L'uscita sinusoidale fornisce lo spettro più pulito di tutte le forme di uscita: idealmente una sola riga spettrale alla frequenza fondamentale. L'ampiezza è specificata come tensione picco-picco (Vpp) o come potenza in dBm. I valori tipici sono da 0,5 a 1,0 Vpp o da 0 a +13 dBm nei sistemi a 50 Ω.

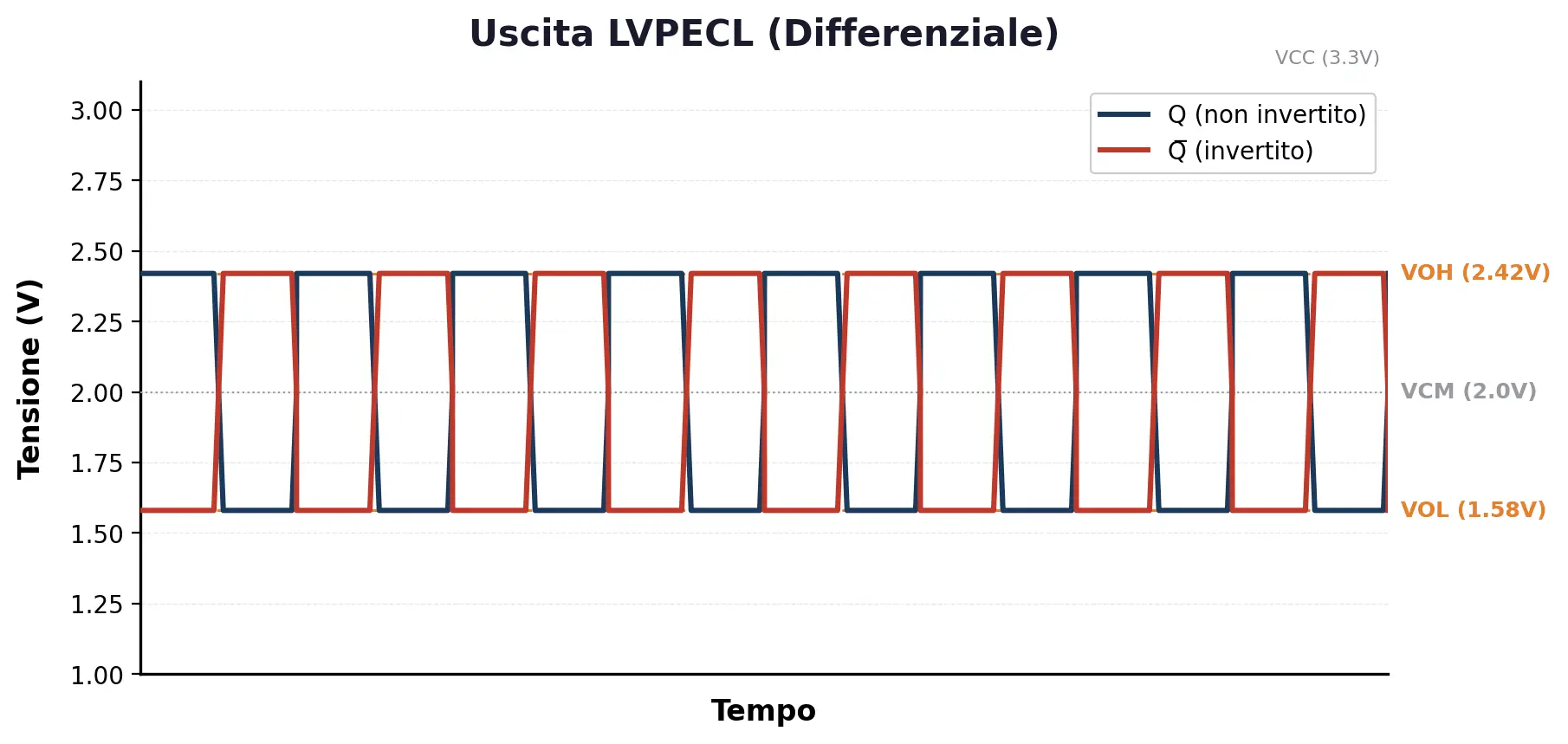

3,5 LVPECL

Fig. 5: Uscita LVPECL – Segnale differenziale con ca. 800 mV di escursione totale attorno a VCC–1,3 V

Il LVPECL utilizza un instradamento del segnale differenziale: due uscite complementari (Q e Q̅) oscillano in controfase attorno a un livello di modo comune (VCM), tipicamente a VCC–1,3 V. L'escursione di tensione differenziale è di ca. 800 mV. L'architettura a sorgente di corrente consente tempi di commutazione estremamente rapidi con tendenza minima all'overshoot.

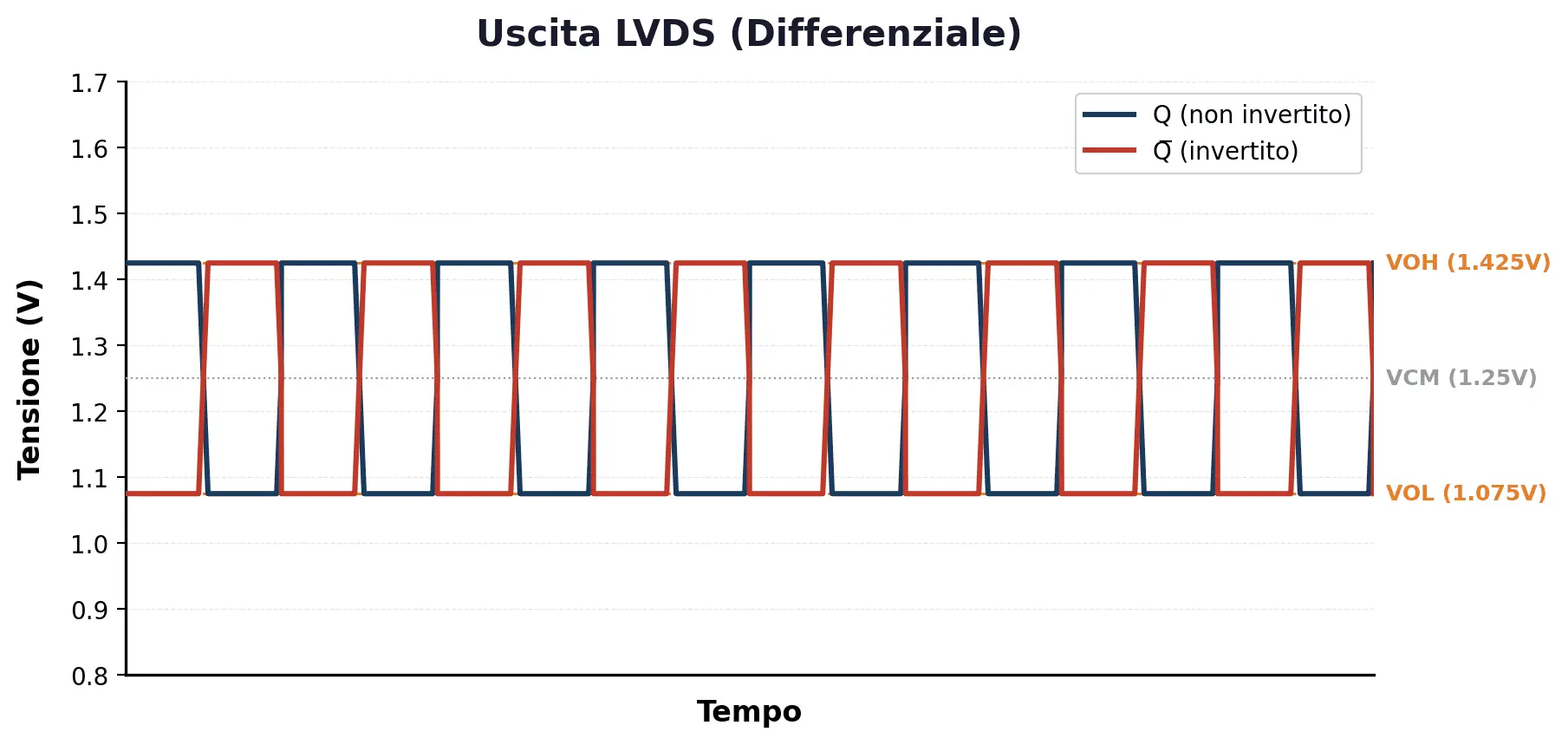

3.6 LVDS

Fig. 6: Uscita LVDS – Segnale differenziale con soli 350 mV di escursione attorno a 1,25 V di livello di modo comune

Il LVDS si caratterizza per la sua escursione di tensione differenziale particolarmente bassa di soli 350 mV. Il livello di modo comune è a 1,25 V. Grazie al driver pilotato in corrente (tipicamente 3,5 mA) e alla terminazione a 100 Ω, si ottiene un'elevata integrità del segnale con un consumo minimo. La bassa ampiezza minimizza le emissioni elettromagnetiche.

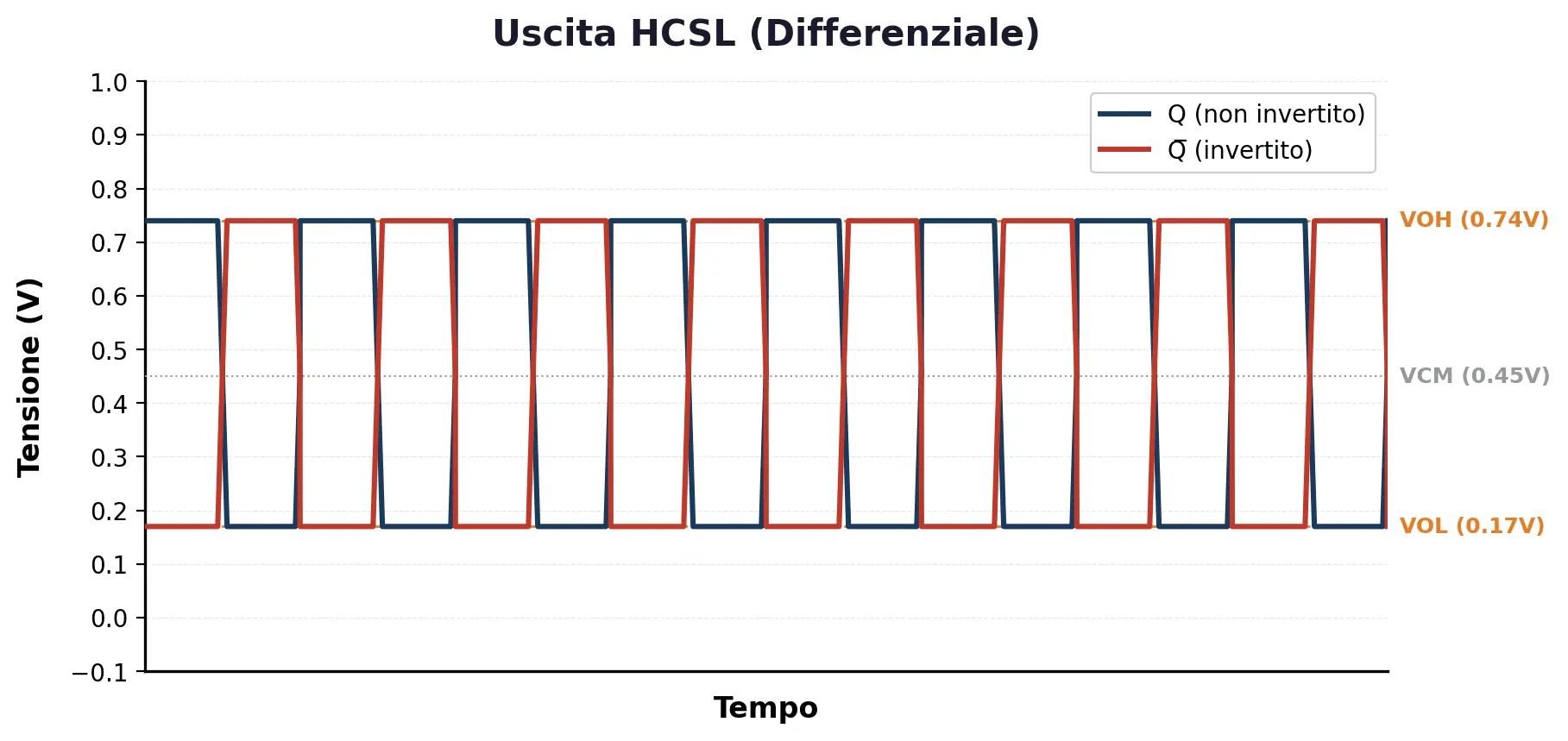

3.7 HCSL

Fig. 7: Uscita HCSL – Segnale differenziale in modalità corrente per clock di riferimento PCIe

L'HCSL opera con un'escursione di tensione molto bassa: VOH è tipicamente 0,74 V e VOL 0,17 V, risultando in un livello di modo comune di ca. 0,45 V. L'architettura di pilotaggio in corrente è specificamente ottimizzata per i requisiti della specifica PCIe e consente un adattamento di impedenza preciso tramite terminazioni da 50 Ω verso massa.

4. Confronto dei segnali di uscita

La seguente tabella riassume le proprietà essenziali di tutti e sette i tipi di uscita:

Typ | Tipo di segnale | VCC (V) | VOH/ VOL (V) | Esc. diff. | Freq. max. ca. | Applicazione tipica |

| CMOS | Single- Ended | 1,8-5,0 | VCC/ 0 | - | ~285 MHz | Microcontrollori, FPGA, tecnica digitale generale |

| TTL | Single- Ended | 1,8-5,0 | 3,4/ 0,3 | - | ~150 MHz | Sistemi legacy, controlli industriali |

| Seno tagliato | Single- Ended | 1,8/2,5/3,3 | variabile | - | ~200 MHz | Telecomunicazioni, applicazioni RF |

| Onda sinusoidale | Single- Ended | 3,3/5,0/12 | variabile | - | >1 GHz | Tecnica RF, strumenti di misura, sintesi di frequenza |

| LVPECL | Differ- enziale | 2,5/3,3 | ~2,4/ ~1,6 | ~800 mV | >3 GHz | Apparecchiature di rete, SONET/SDH, clocking ad alta velocità |

| LVDS | Differ- enziale | 2,5/3,3 | ~1,43/ ~1,07 | 350 mV | >1 GHz | Interfacce display, collegamenti seriali, clocking FPGA |

| HCSL | Differ- enziale | 3,3 | 0,74/ 0,17 | ~570 mV | ~200 MHz | Clock di riferimento PCI Express (100 MHz) |

5. Differenze essenziali in dettaglio

5.1 Single-Ended vs. Differenziale

La differenza più fondamentale tra i tipi di uscita è l'instradamento del segnale. CMOS, TTL, Clipped Sine Wave e Sinus sono segnali single-ended – sono riferiti a una massa comune. LVPECL, LVDS e HCSL invece sono segnali differenziali con due linee complementari. I segnali differenziali offrono vantaggi decisivi alle frequenze più elevate: sopprimono i disturbi di modo comune, consentono escursioni di tensione più piccole e permettono così tempi di commutazione più rapidi con minori emissioni elettromagnetiche.

5.2 Escursione di tensione e margine di rumore

Il CMOS offre la maggiore escursione di tensione assoluta con la sua uscita rail-to-rail e quindi il miglior margine di rumore statico. Il TTL ha un margine di rumore più limitato a causa dei suoi livelli asimmetrici. Gli standard differenziali (LVPECL, LVDS, HCSL) compensano le loro escursioni di tensione più ridotte con la reiezione di modo comune della trasmissione differenziale, rendendoli spesso più affidabili in ambienti disturbati rispetto ai segnali single-ended.

5.3 Consumo di corrente

Gli oscillatori CMOS consumano praticamente nessuna corrente allo stato statico; il consumo aumenta proporzionalmente con la frequenza (dissipazione dinamica). Il TTL ha un consumo di corrente a riposo costantemente più elevato a causa dell'architettura bipolare. Il LVPECL richiede resistenze di terminazione esterne e ha il consumo più elevato degli standard differenziali. Il LVDS è noto per il suo basso consumo (tipicamente 3,5 mA di corrente del driver). L'HCSL si colloca tra LVDS e LVPECL in termini di consumo.

5.4 Gamma di frequenze e aree di applicazione

Per frequenze fino a circa 200 MHz, gli oscillatori CMOS rappresentano la prima scelta nella maggior parte dei casi grazie alla loro versatilità, alla semplicità di progettazione dei circuiti e all'ampia disponibilità. Oltre i 200 MHz circa, si consigliano uscite differenziali. LVPECL offre le frequenze più elevate (>3 GHz) ed è utilizzato in apparecchiature di rete e telecomunicazioni. LVDS copre un'ampia gamma di frequenze medie ed è particolarmente comune nelle applicazioni FPGA e display. HCSL è ottimizzato per il suo caso d'uso di nicchia: il clock di riferimento a 100 MHz per PCI Express.

5.5 Terminazione e complessità del circuito

Le uscite CMOS e TTL generalmente non richiedono terminazione esterna per brevi lunghezze di pista – questo le rende particolarmente semplici nell'utilizzo. Il LVPECL richiede obbligatoriamente resistenze di terminazione esterne (tipicamente: terminazione Thévenin verso VCC–2 V o resistenze verso massa), aumentando la complessità del circuito. Il LVDS viene terminato di default con una resistenza differenziale da 100 Ω al ricevitore. L'HCSL utilizza resistenze da 50 Ω verso massa su ogni uscita.

6. Overshoot nei segnali di uscita degli oscillatori

6.1 Cosa sono gli overshoot?

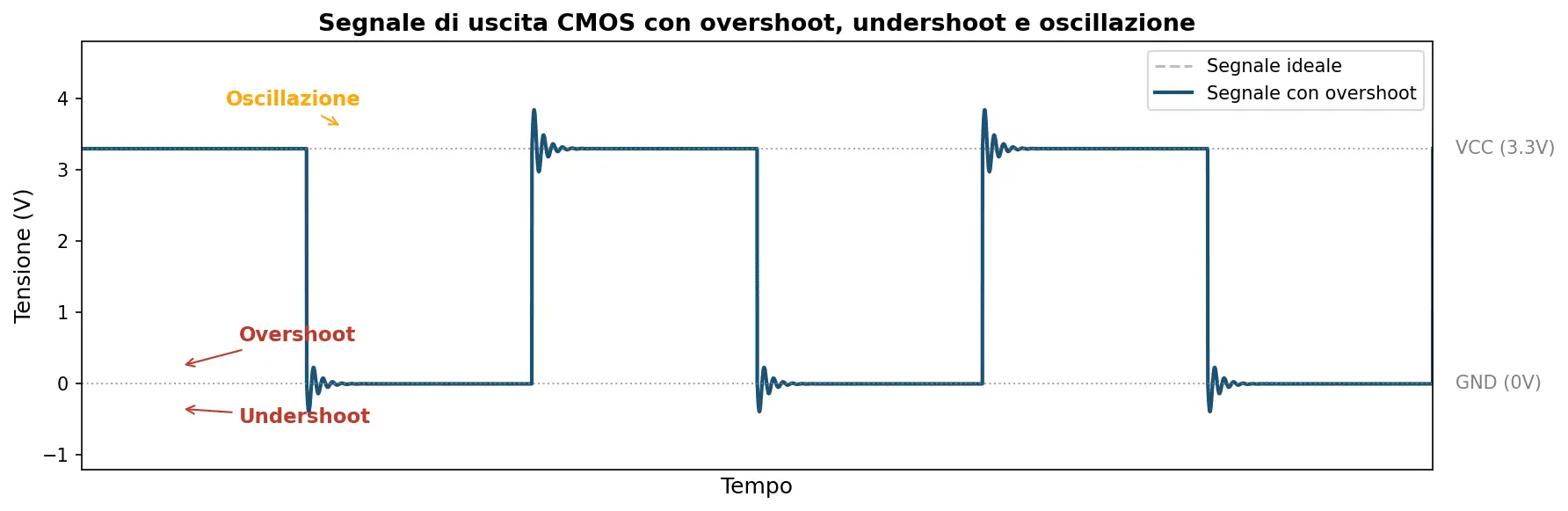

Overshoot e undershoot sono brevi picchi di tensione che si verificano durante le operazioni di commutazione rapida. Su un fronte di salita, la tensione supera brevemente VCC (overshoot), mentre su un fronte di discesa, scende leggermente al di sotto di GND (undershoot). Questi picchi sono spesso seguiti da oscillazioni smorzate note come "ringing".

La causa risiede nella combinazione dei fronti di commutazione molto ripidi del driver di uscita e delle induttanze e capacità parassite della pista, del package e della capacità di carico. Fisicamente si forma un circuito risonante dall'induttanza della linea e dalla capacità di ingresso del ricevitore. Più ripido è il fronte di commutazione e più lunga è la pista, più pronunciato è l'overshoot.

Fig. 8: Segnale di uscita CMOS con overshoot – Overshoot sopra VCC, undershoot sotto GND e ringing successivo

6.2 Perché gli overshoot sono problematici?

Gli overshoot che superano VCC o scendono sotto GND possono polarizzare in conduzione diretta i diodi di protezione ESD del circuito ricevitore, generando correnti parassite. Nel caso peggiore ciò può portare a un latch-up – un flusso di corrente incontrollato attraverso strutture tiristore parassite nel circuito CMOS, che può distruggere il componente. Un forte ringing può inoltre causare trigger multipli agli ingressi di clock quando la tensione attraversa la soglia di commutazione più volte, portando a un comportamento di sistema errato.

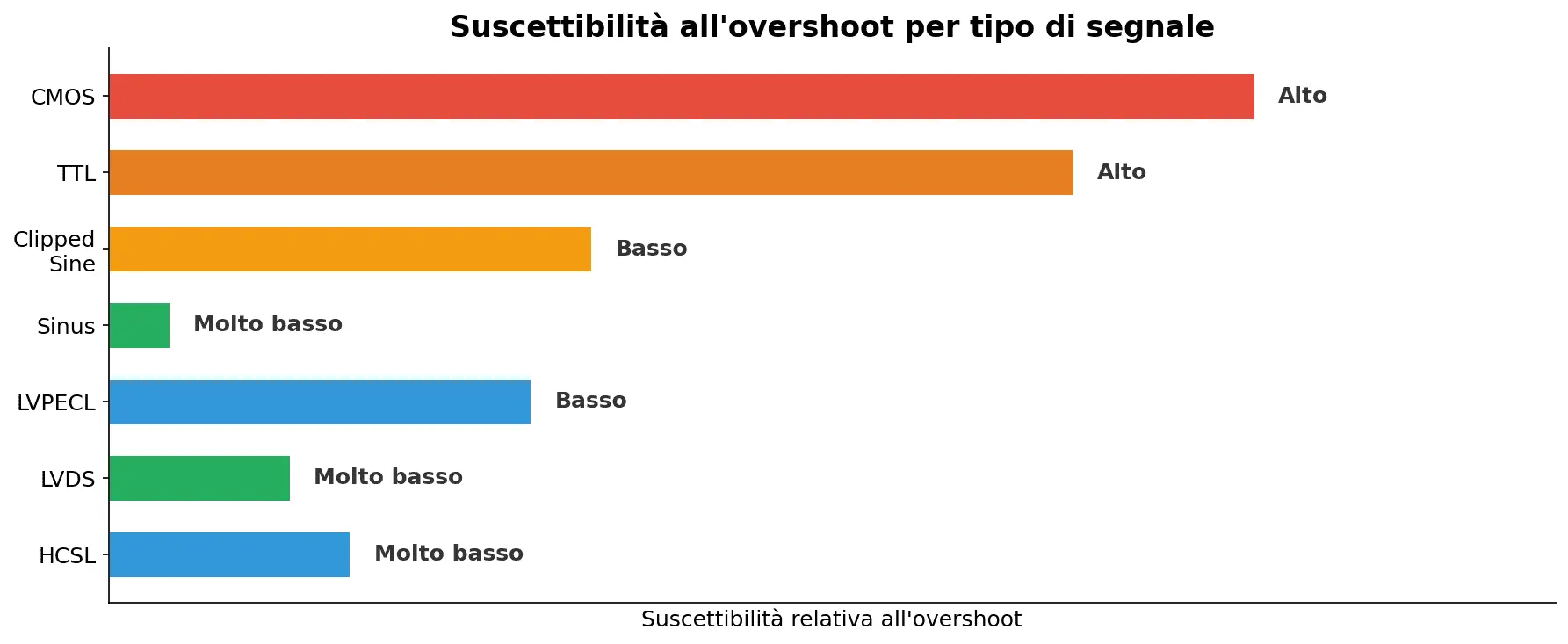

6.3 Confronto: overshoot per tipo di segnale

La suscettibilità all'overshoot differisce notevolmente tra i diversi tipi di uscita. Il seguente grafico mostra la suscettibilità relativa a confronto:

6.4 Overshoot nei segnali single-ended

CMOS: Più colpito. I driver MOSFET simmetrici canale P/canale N generano fronti molto ripidi che, combinati con le induttanze di pista, causano overshoot pronunciati. Soprattutto con i moderni oscillatori CMOS a bassa tensione (1,8 V), gli overshoot possono essere significativi rispetto alla tensione di alimentazione.

TTL: Anch'esso suscettibile, anche se per ragioni leggermente diverse. Lo stadio di uscita asimmetrico totem-pole genera un breve picco di corrente sul fronte di salita quando entrambi i transistor conducono simultaneamente (cross-conduction). I fronti tipicamente un po' più lenti rispetto al CMOS moderno attenuano leggermente il problema.

Clipped Sine Wave: Significativamente meno suscettibile. I picchi di ampiezza limitati e i fronti comparativamente morbidi producono molta meno energia ad alta frequenza che potrebbe eccitare riflessioni e ringing. Il clipping agisce come un limitatore di ampiezza naturale che sopprime l'overshoot già nel segnale.

Onda sinusoidale: Praticamente immune al classico overshoot. Poiché il segnale non presenta brusche transizioni di fronte, non viene generato alcun impulso di energia a banda larga che potrebbe eccitare risonanze di linea. Tuttavia, disallineamenti di impedenza possono portare a onde stazionarie e riflessioni che alterano l'ampiezza del segnale in determinati punti. Questo è controllato dalla classica terminazione RF (terminazione a 50Ω o 75Ω).

6.5 Overshoot nei segnali differenziali

LVPECL: Intrinsecamente ben soppresso grazie allo stadio di uscita a sorgente di corrente. Il pilotaggio in corrente limita naturalmente la pendenza massima dei fronti. Con una terminazione insufficiente possono comunque verificarsi riflessioni, poiché il LVPECL opera a frequenze molto elevate. Il circuito Thévenin o inseguitore di emettitore corretto è qui decisivo – non principalmente a causa dell'overshoot, ma per garantire il punto di lavoro corretto ed evitare riflessioni.

LVDS: Molto robusto per costruzione. Il driver pilotato in corrente fornisce una corrente costante di tipicamente 3,5 mA nella terminazione differenziale a 100 Ω, limitando fisicamente l'escursione di tensione. Anche con discontinuità di impedenza, le riflessioni rimangono piccole poiché la bassa escursione di tensione di soli 350 mV fornisce poca energia per i disturbi. Il LVDS è uno degli standard più tolleranti per quanto riguarda l'integrità del segnale.

HCSL: Si comporta in modo simile al LVDS grazie all'architettura basata sulla corrente. La bassissima escursione di tensione e la terminazione a 50 Ω verso massa garantiscono un adattamento di impedenza pulito. Nella specifica PCIe, l'overshoot ammissibile è esplicitamente definito e strettamente tolleranzato, cosicché gli oscillatori conformi HCSL soddisfano intrinsecamente questi requisiti.

6.6 Contromisure per il controllo dell'overshoot

La misura più efficace per i segnali single-ended (in particolare CMOS e TTL) è una resistenza in serie direttamente all'uscita dell'oscillatore, tipicamente nell'intervallo da 22 a 47 Ω. Questa resistenza forma insieme all'impedenza della pista un partitore di tensione che smorza il fronte e assorbe le riflessioni. Il valore ottimale risulta dalla differenza tra l'impedenza della pista e l'impedenza di uscita del driver.

Inoltre sono utili piste corte a impedenza controllata, la minimizzazione dei via sulla linea di clock, un piano di massa continuo sotto la linea del segnale e condensatori di disaccoppiamento sufficienti vicino all'oscillatore (tipicamente 100 nF ceramici più 10 µF). Alcuni produttori di oscillatori CMOS offrono inoltre modelli con controllo della pendenza dei fronti (Slew Rate Control) che attenuano il problema già nel driver.

Per i segnali differenziali (LVPECL, LVDS, HCSL), la terminazione corretta e conforme alle specifiche è la misura più importante. Inoltre, le due linee di una coppia differenziale dovrebbero essere sempre instradate con lunghezza uguale e accoppiamento stretto per minimizzare lo skew (differenze di tempo di propagazione) e mantenere la reiezione di modo comune.

7. Guida alla decisione

La scelta del tipo di uscita corretto dipende essenzialmente da quattro fattori: la frequenza di clock richiesta, la famiglia logica del ricevitore, il budget di potenza disponibile e i requisiti di integrità del segnale.

Caso applicativo | Raccomandazione |

| Tecnica digitale generale, µC, FPGA I/O (fino a ~200 MHz) | CMOS – Soluzione più semplice ed economica, rail-to-rail, massima disponibilità, flessibile nella tensione di alimentazione (1,8–5,0 V) |

| Sistemi legacy 5V, controlli industriali | TTL – Direttamente compatibile con le famiglie logiche 5V più vecchie; sempre più sostituito dal CMOS con alimentazione 5V |

| Applicazioni RF, circuiti a trasformatore | Clipped Sine Wave o Sinus – Un minor contenuto di armoniche riduce i problemi EMC e consente una sintesi di frequenza precisa |

| Apparecchiature di rete ad alta velocità (>622 MHz) | LVPECL – Massima velocità di commutazione, ideale per SONET/SDH, Ethernet PHY e clock backplane |

| Clocking FPGA, trasmissione dati seriale, interfacce display | LVDS – Compromesso ottimale tra velocità, consumo e comportamento EMC |

| Clock di riferimento PCI Express | HCSL – Unico standard di clock specificato dal PCI-SIG per i sistemi PCIe |