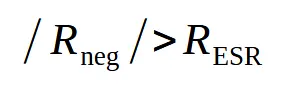

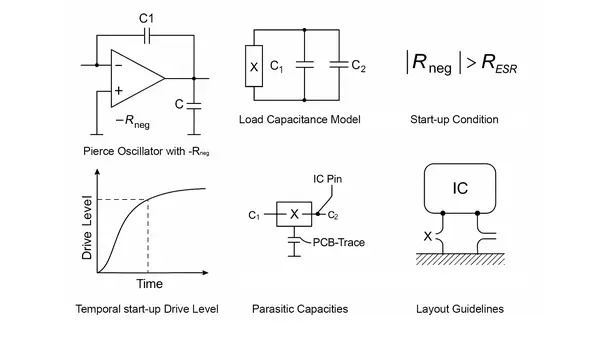

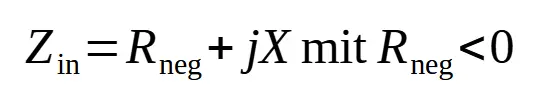

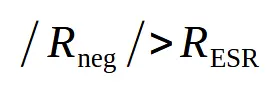

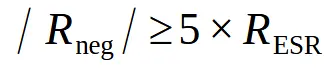

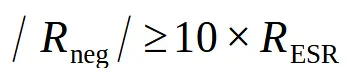

Ciò significa che il valore della resistenza di ingresso negativa deve essere maggiore della resistenza in serie (ESR) del cristallo.

Solo in questo caso si avrà un'amplificazione netta che porterà all'oscillazione.

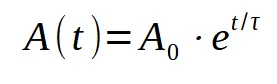

F.2: Influenza sulla sicurezza della risposta transitoria

Se il valore della resistenza di ingresso negativa è troppo piccolo (cioè -Rneg è troppo debole), si verifica quanto segue:

- Il cristallo riceve troppa poca energia → oscillazione lenta o nulla

- L'oscillazione si avvia solo con una tensione di alimentazione o una temperatura più elevata.

- L'avvio in modalità operative a basso consumo diventa inaffidabile.

Causa tipica:

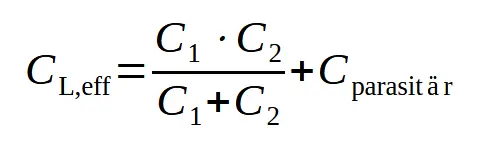

Alcuni MCU moderni hanno amplificatori oscillatori deboli per motivi di efficienza, il che significa che -Rneg è minore rispetto alle vecchie generazioni di circuiti integrati. Allo stesso tempo, molti progetti lavorano con piccole capacità di carico o lunghe tracce, il che aumenta le perdite parassite.

D.3: Perché i cristalli con bassa ESR sono particolarmente importanti?

La VES del cristallo definisce le sue perdite interne. Una bassa ESR significa

- minori perdite

- minore contro-amplificazione necessaria

- elevata stabilità ai transienti anche con stadi oscillatori deboli

- tempo di avvio più breve

- oscillazione più stabile in funzione della temperatura

Raccomandazioni pratiche:

- Utilizzare cristalli la cui ESR è significativamente inferiore al valore massimo specificato dal circuito integrato.

- Se un microcontrollore specifica una ESR massima di 70 Ω, ad esempio, è ideale un cristallo con una ESR di 30-50 Ω. Questo lascia un margine di sicurezza sufficiente contro un'eventuale bassa resistenza d'ingresso negativa dell'oscillatore.

F.4: Conclusione sull'interazione tra -Rneg e ESR del quarzo

L'affidabilità della risposta transitoria dipende essenzialmente da quanto segue:

- l'oscillatore interno fornisce una resistenza di ingresso negativa sufficiente,

- il cristallo ha una ESR sufficientemente bassa,

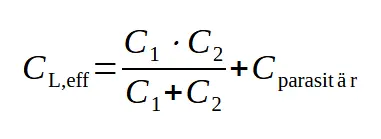

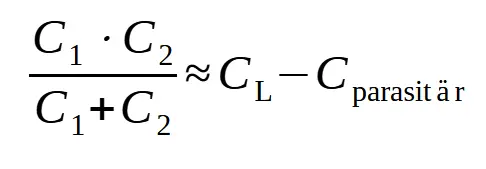

- le capacità di carico sono dimensionate correttamente.

Solo se il rapporto tra -Rneg e ESR è corretto, il cristallo si avvia rapidamente, in modo affidabile e per l'intero intervallo di temperatura e tensione.